# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

### **Under Development**

SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

#### Description

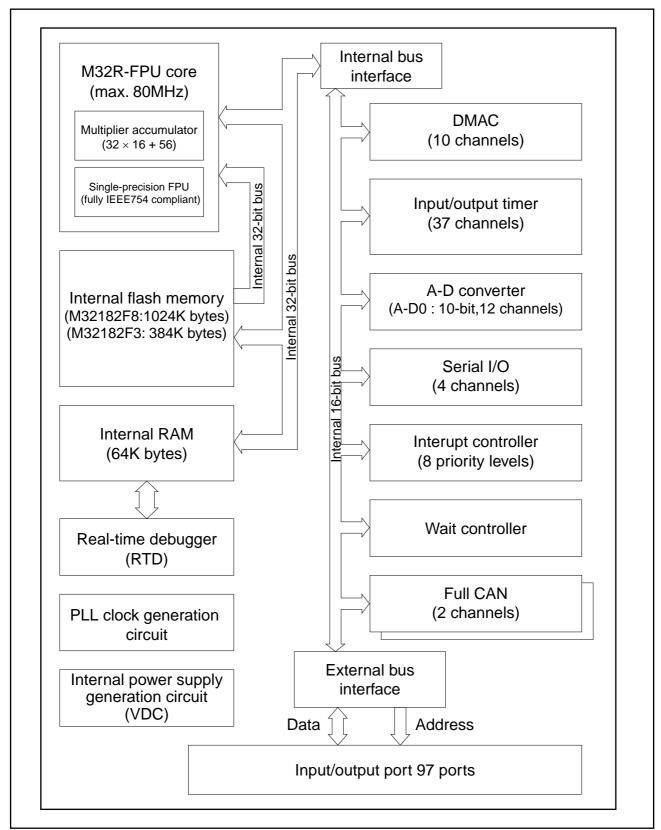

The 32182 Group is a 32-bit, single-chip RISC microcomputer with built-in flash memory, which was developed for use in general industrial and household equipment. To accomplish high-precision arithmetic operations, it incorporates a fully IEEE754 compliant, single-precision FPU.

This microcomputer contains a variety of peripheral functions ranging from 12-channel A-D converters, 37-channel multijunction timers, 10-channel DMACs, 4-channel serial I/Os, and 1-channel Real-time Debugger. Also included are 2-channel Full-CAN modules and JTAG (boundary scan facility). With the software necessary to run these numerous peripheral functions stored in its large-capacity flash memory, this microcomputer meets the needs of application systems for high functionality, high-performance arithmetic capability, and sophisticated control.

With lower power consumption and low noise characteristics also considered, these microcomputers are ideal for embedded equipment applications.

#### **Features**

M32R-FPU core

- Uses the M32R family RISC CPU core (M32R family common instruction set + single-precision FPU/extended instructions)

- Five-stage pipelined processing

- Sixteen 32-bit general-purpose registers

- 16-bit/32-bit instructions implemented

- DSP function instructions (multiply-Accumulate calculation using 56-bit accumulator)

- Built-in single-precision FPU (fully compliant with IEEE754 standard: four rounding modes, etc.)

- Bit manipulation extended instructions

- · Built-in flash memory

- · Built-in flash programming boot program

- Built-in RAM

- PLL clock generating circuit...... Multiply by 8

- Oscillation stop detection function

- Maximum operating frequency of the CPU clock M32182F8VFP/M32182F3VFP

......64MHz (when operating at -40°C to +125°C) M32182F8TFP/M32182F3TFP

......80MHz (when operating at -40°C to +85°C)

• Single power supply: 5 V (<u>+</u> 0.5 V) or 3.3 V (<u>+</u> 0.3 V)

Table 1. Type Name List (32182 Group)

| Type Name               | RAM Size  | ROM Size    |

|-------------------------|-----------|-------------|

| M32182F8VFP/M32182F8TFP | 64K bytes | 1024K bytes |

| M32182F3VFP/M32182F3TFP | 64K bytes | 384K bytes  |

#### 37-channel multijunction timers (MJT)

Multijunction timers are incorporated that support various purposes of use.

| 16-bit output related timers (TOP) 11 channels       |

|------------------------------------------------------|

| 16-bit input/output related timers (TIO) 10 channels |

| 16-bit input related timers (TMS) 8 channels         |

| 32-bit input related timers (TML) 8 channels         |

- Flexible configuration is possible through interconnection of timers.

- The internal DMAC and A-D converter can be started by a timer.

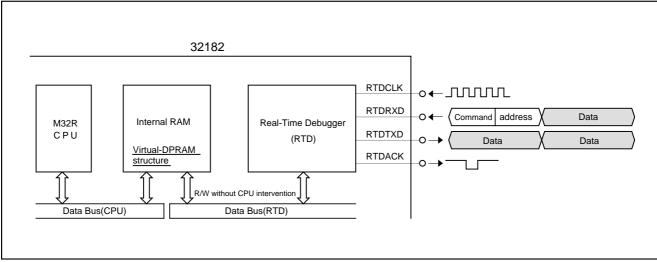

#### Real-time Debugger

- Includes dedicated clock-synchronized serial I/O that can read and write the contents of the internal RAM independently of the CPU.

- Can look up and update the data table in real time while the program is running.

- Can generate a dedicated interrupt based on RTD communication.

### Abundant internal peripheral functions

In addition to the timers and real-time debugger, the microcomputer contains the following peripheral functions.

- DMAC ...... 10 channels

- A-D converters (Sample & hold function, Disconnection detector assist function, Injection current bypass circuit)

- Interrupt controller: 23 interrupt sources, 8 priority levels

- Wait controller

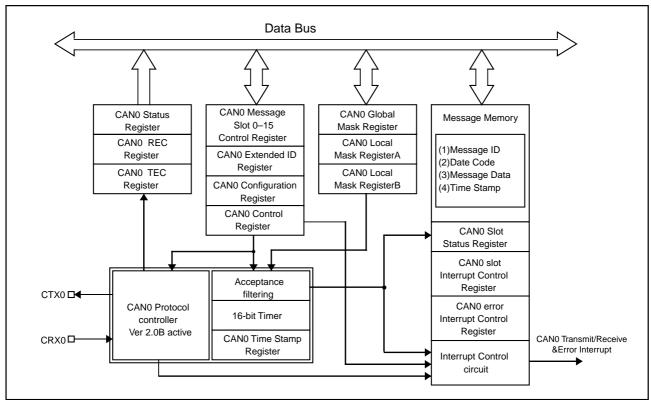

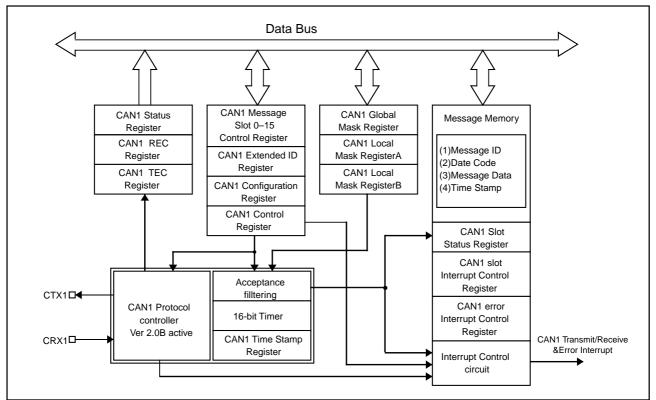

- Full CAN (CAN Specification 2.0B active)....... 2 channels

- Virtual-Flash emulation function ........ 4K bytes × 8 banks

- JTAG (boundary scan function, Mitsubishi original SDI debug function)

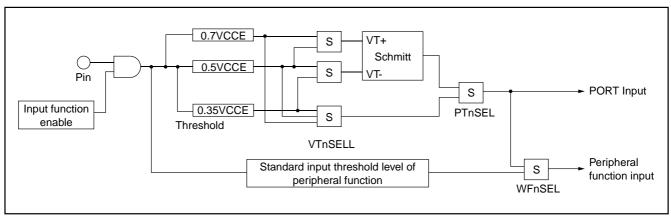

- Port input threshold level select function

### Designed to operate at high temperatures

To meet the need for use at high temperatures, the microcomputer is designed to be able to operate in the temperature range of -40 to +125°C when CPU clock operating frequency = 64 MHz. When CPU clock operating frequency = 80 MHz, the microcomputer can be used in the temperature range of -40 to +85°C.

Note: • This does not guarantee continuous operation at 125°C. If you are considering use of the microcomputer at 125°C, please consult Mitsubishi.

### **Applications**

Automobile equipment control (e.g., Engine, ABS, and AT), industrial equipment system control, and high-function OA equipment (e.g., PPC)

### **Under Development**

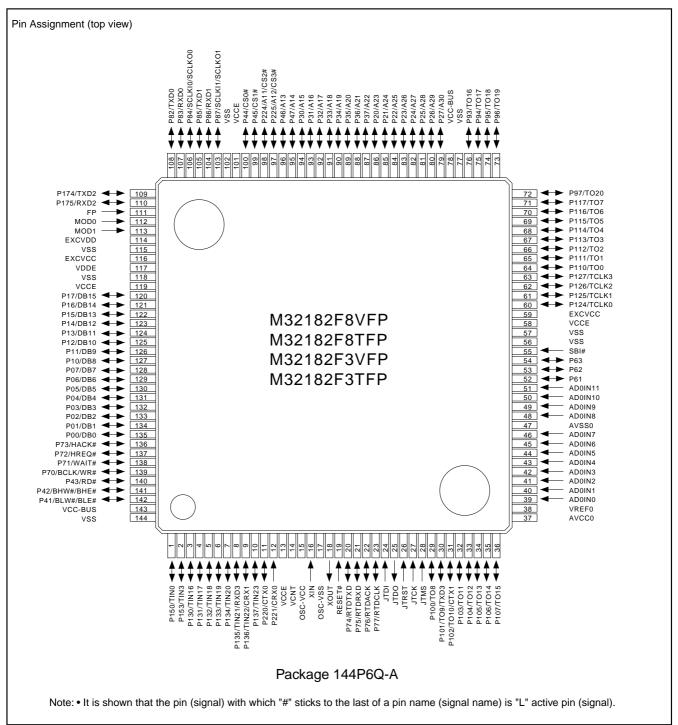

Figure 1. Pin Layout Diagram

## **Under Development**

Figure 2. Block diagram

## **Under Development**

| Functional Block     | Features                                                                                                       |

|----------------------|----------------------------------------------------------------------------------------------------------------|

| M32R-FPU core        | M32R family CPU core, internally configured in 32-bit                                                          |

|                      | Built-in multiplier-accumulator (32 × 16 + 56)                                                                 |

|                      | Basic bus cycle: 15.625 ns (CPU clock frequency at 64 MHz, Internal peripheral clock frequency at 16MHz)       |

|                      | : 12.5 ns (CPU clock frequency at 80 MHz, Internal peripheral clock frequency at 20MHz)                        |

|                      | Logical address space: 4G bytes, linear                                                                        |

|                      | General-purpose register: 32-bit register $\times$ 16,Control register: 32-bit register $\times$ 6             |

|                      | Accumulator: 56-bit                                                                                            |

| External data bus    | 16-bit data bus                                                                                                |

| Instruction set      | 16-bit/32-bit instruction formats                                                                              |

|                      | 100 discrete instructions in six addressing modes                                                              |

| Internal flash mem-  | M32182F8VFP/M32182F8TFP: 1024K bytes                                                                           |

| ory                  | M32182F3VFP/M32182F3TFP: 384K bytes                                                                            |

|                      | Rewrite durability: 100 times                                                                                  |

| Internal RAM         | 64K bytes                                                                                                      |

| DMAC                 | 10 channels (DMA transfers between internal peripheral I/Os, between internal peripheral I/O and internal      |

|                      | RAM, and between internal RAMs)                                                                                |

|                      | Channels can be cascaded and can operate in combination with internal peripheral I/O                           |

| Multijunction timer  | 37 channels of multijunction timers.                                                                           |

|                      | TOP: 16-bit output related timer, 11 channels (single-shot, delayed single-shot, and continuous)               |

|                      | TIO :16-bit input/output related timer, 10 channels (measure clear, measure free-run, noise processing         |

|                      | input, PWM, single-shot, delayed single-shot, continuous output)                                               |

|                      | TMS: 16-bit input related timer, 8 channels (measure input)                                                    |

|                      | TML: 32-bit input related timer, 8 channels (measure input)                                                    |

|                      | Flexible timer configuration is possible through interconnection of channels using the clock bus or event bus. |

| A-D converter        | 10-bit multifunction A-D converters                                                                            |

|                      | • Input 12 channels                                                                                            |

|                      | <ul> <li>Scan-based conversion can be switched between N (N = 1-12) channels</li> </ul>                        |

|                      | Capable of interrupt conversion during scan                                                                    |

|                      | 8-bit/10-bit readout function                                                                                  |

|                      | Sample & hold function                                                                                         |

|                      | Disconnection detector assist function                                                                         |

|                      | Injection current bypass circuit                                                                               |

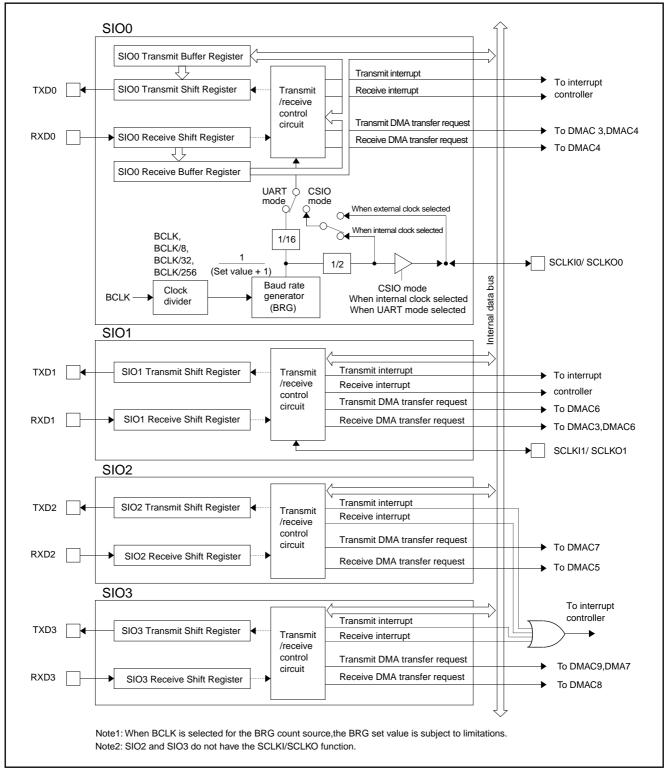

| Serial I/O           | 4 channels (The serial I/Os can be set for synchronous serial I/O or UART.                                     |

|                      | SIO2, SIO3 are UART mode only)                                                                                 |

| Real-time Debugger   | 1-channels dedicated clock-synchronized serial                                                                 |

| (RTD)                | Entire area of internal RAM                                                                                    |

|                      | Can access the internal RAM for read/rewrite from outside independently of the CPU, and also generate          |

|                      | an exclusive-use interrupt.                                                                                    |

| Interrupt controller | Controls interrupts from internal peripheral I/Os                                                              |

|                      | (Priority can be set to one of 8 levels including interrupt disabled)                                          |

| Wait controller      | Controls wait when accessing external extended area                                                            |

|                      | (Chip selects for four external extended areas each can have access extended for 0–7 wait cycles plus          |

|                      | WAIT# signal entered from external source) (Note 1)                                                            |

| CAN                  | Two channels, each having 16-channel message slots                                                             |

| JTAG                 | Boundary-Scan function, Built-in SDI debugger function in MITSUBISHI                                           |

| Clock                | M32182F8VFP, M32182F3VFP:                                                                                      |

|                      | CPU clock: maximum 64 MHz (for CPU, internal ROM, and internal RAM access)                                     |

|                      | Internal peripheral clock (BCLK): maximum 16 MHz (for peripheral module access)                                |

|                      | External input clock (XIN): maximum 8.0 MHz, built-in ×8 PLL circuit                                           |

|                      | M32182F8TFP, M32182F3TFP:                                                                                      |

|                      | CPU clock: maximum 80 MHz (for CPU, internal ROM, and internal RAM access)                                     |

|                      | Internal peripheral clock (BCLK): maximum 20 MHz (for peripheral module access)                                |

|                      | External input clock (XIN): maximum 10.0 MHz, built-in ×8 PLL circuit                                          |

## **Under Development**

SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

**Table 2. Outline Performance (2/2)**

| Functional Block   | Features                                                                                            |

|--------------------|-----------------------------------------------------------------------------------------------------|

| Power Supply Volt- | 5V (± 0.5V) or 3.3V (± 0.3V) [T.B.D]: single power supply voltage (The internal logic operates with |

| age                | 2.5 V, however)                                                                                     |

| Operating tempera- | M32182F8VFP, M32182F3VFP:                                                                           |

| ture range         | -40 to +125°C (CPU clock 64MHz, internal peripheral clock 16MHz)                                    |

| (Note 2)           | M32182F8TFP, M32182F8TFP:                                                                           |

|                    | -40 to +85°C (CPU clock 80MHz, internal peripheral clock 20MHz)                                     |

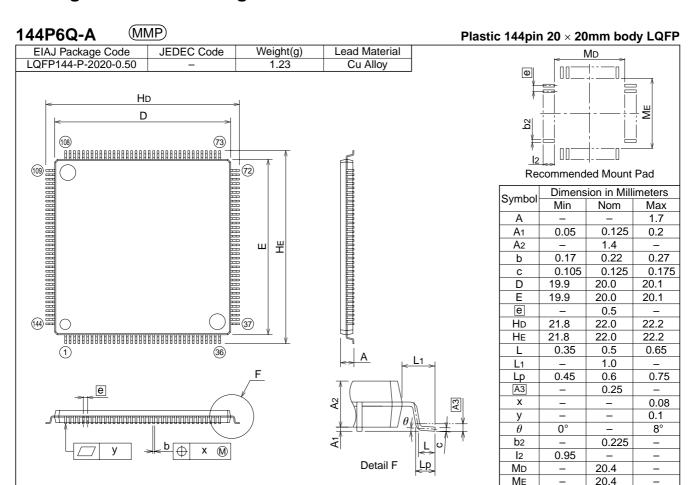

| Package            | 0.5mm pitches / 144-pin LQFP package (144P6Q-A)                                                     |

Note 1: Wait Cycle by the external WAIT# input is not received when 0wait is selected. Moreover, as for all idol setup after the wait / strike robe / recovery / lead of CS block, only operation by "nothing" setup is guaranteed when 0wait is selected.

Note 2: This does not mean that the microcomputer is guaranteed for continuous operation at 125°C. If 125°C applications are desired, please consult Mitsubishi.

## **Under Development**

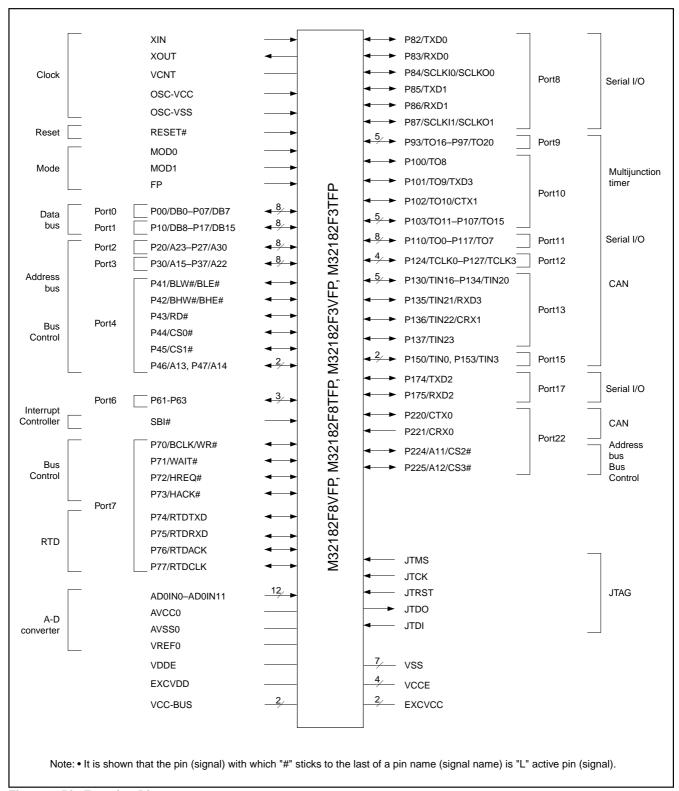

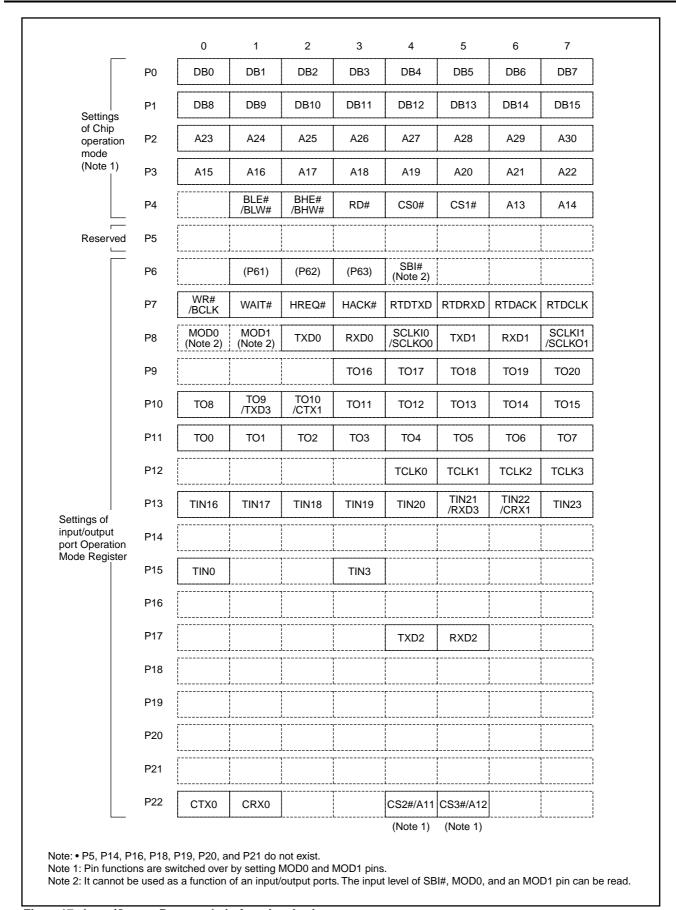

Figure 3. Pin Function Diagram

## **Under Development**

### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

| Table 3  | Description | of Din | Function | /1/3\ |

|----------|-------------|--------|----------|-------|

| Table 5. | Describtion | OI PIN | runction | (1/3) |

| Туре                                                                            | Pin       | Name                              | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                    |                                                                                |                                                                                                      |  |  |  |

|---------------------------------------------------------------------------------|-----------|-----------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Power                                                                           | VCCE      | Power supply                      | -            | Power supply (5.0V $\pm$ 0.5V or 3.3V $\pm$ 0.3V).                                                                                                                                                                                                                                                                                                                          |                                                                                |                                                                                                      |  |  |  |

| Supply EXCVCC External capaci External capacitance connecting pin tance connect |           |                                   |              |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | connecting pin.                                                                                      |  |  |  |

|                                                                                 | VCC-BUS   | Bus power supply                  | -            | Power supply for the bus control pins (5.0V $\pm$ 0.5V or 3.3V $\pm$ 0.3V).                                                                                                                                                                                                                                                                                                 |                                                                                |                                                                                                      |  |  |  |

|                                                                                 | VDDE      | RAM power supply                  | -            | Internal RAM backup power supply (5.0V ± 0.5V or 3.3V ± 0.3V).                                                                                                                                                                                                                                                                                                              |                                                                                |                                                                                                      |  |  |  |

|                                                                                 | EXCVDD    | External capaci-<br>tance connect | -            | Backup pov                                                                                                                                                                                                                                                                                                                                                                  | Backup power supply for the internal RAM, external capacitance connecting pin. |                                                                                                      |  |  |  |

|                                                                                 | VSS       | Ground                            | =            |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | to ground (GND).                                                                                     |  |  |  |

| Clock                                                                           | XIN       | Clock input                       | Input        |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | ns. These pins contain a PLL-based frequency                                                         |  |  |  |

|                                                                                 | XOUT      | Clock output                      | Output       | multiply-by-8, so input the clock whose frequency is 1/8 the operating frequency. (XIN input = 10 MHz when CPU clock operates at 80 lb.)                                                                                                                                                                                                                                    |                                                                                |                                                                                                      |  |  |  |

| BCLK                                                                            |           | System clock                      | Output       | Outputs a clock twice the externally sourced clock frequency, XIN (when the internal CPU memory clock is 80 MHz, BCLK output = 20 MHz).  Use this output when external sync design is desired.                                                                                                                                                                              |                                                                                |                                                                                                      |  |  |  |

|                                                                                 | OSC-VCC   | Clock power supply                | -            | Power supply to the PLL circuit. Connect OSC-VCC to the power supply                                                                                                                                                                                                                                                                                                        |                                                                                |                                                                                                      |  |  |  |

|                                                                                 | OSC-VSS   | Clock ground                      | =            | Connect OSC-VSS to ground.                                                                                                                                                                                                                                                                                                                                                  |                                                                                |                                                                                                      |  |  |  |

|                                                                                 | VCNT      | PLL control                       | -            | This pin controls the PLL circuit. Connect a resistor and pin.                                                                                                                                                                                                                                                                                                              |                                                                                |                                                                                                      |  |  |  |

| Reset                                                                           | RESET#    | Reset                             | Input        | •                                                                                                                                                                                                                                                                                                                                                                           | sets the int                                                                   | ternal circuits.                                                                                     |  |  |  |

| Mode                                                                            | MOD0,     | Mode                              | Input        | •                                                                                                                                                                                                                                                                                                                                                                           |                                                                                | eration mode.                                                                                        |  |  |  |

|                                                                                 | MOD1      |                                   |              | MOD0                                                                                                                                                                                                                                                                                                                                                                        | MOD1                                                                           | Mode                                                                                                 |  |  |  |

|                                                                                 |           |                                   |              | 0                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                              | Single-chip mode                                                                                     |  |  |  |

|                                                                                 |           |                                   |              | 0                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                              | Expanded external mode                                                                               |  |  |  |

|                                                                                 |           |                                   |              | 1                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                              | Processor mode                                                                                       |  |  |  |

|                                                                                 |           |                                   |              |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | (Boot mode) (Note 1)                                                                                 |  |  |  |

|                                                                                 |           |                                   |              | 1                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                              | (Do not select)                                                                                      |  |  |  |

|                                                                                 |           |                                   |              | Note: In boot mode, the FP pin must be at the high level.                                                                                                                                                                                                                                                                                                                   |                                                                                |                                                                                                      |  |  |  |

| Flash-only                                                                      | FP        | Flash Protect                     | Input        |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | flash memory against E/W in hardware.                                                                |  |  |  |

| Address                                                                         | A11–A30   | Address bus                       | Output       |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | of up to 2 MB memory space each to be added                                                          |  |  |  |

| Bus                                                                             |           |                                   |              |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | ress (A11–A30) is provided. A31 is not output.                                                       |  |  |  |

| Data bus                                                                        | DB0-DB15  | Data bus                          | Input/output | This is a 16-bit data bus connecting to an external device. During write cycle, the microcomputer outputs BHW# or BLW# to indicate the valid byte write position of the 16-bit data bus. During read cycle, the microcomputer always reads the full 16-bit data bus. Transferred to the internal circuit of the M32R, however, is the data at only the valid byte position. |                                                                                |                                                                                                      |  |  |  |

| Bus                                                                             | CS0#-CS3# | Chip select                       | Output       |                                                                                                                                                                                                                                                                                                                                                                             | signals fo                                                                     | or external devices.                                                                                 |  |  |  |

| Control                                                                         | RD#       | Read                              | Output       | -                                                                                                                                                                                                                                                                                                                                                                           | -                                                                              | when reading external devices.                                                                       |  |  |  |

|                                                                                 | WR#       | Write                             | Output       |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                | when writing external devices.                                                                       |  |  |  |

|                                                                                 | BHW#      | Byte High Write                   | Output       | U                                                                                                                                                                                                                                                                                                                                                                           |                                                                                | sitions to which valid are transferred when writing                                                  |  |  |  |

|                                                                                 | BLW#      | Byte Low Write                    | Output       | upper addre                                                                                                                                                                                                                                                                                                                                                                 | ess side ([                                                                    | BHW#/ BHE# and BLW#/ BLE# correspond to the DB0-DB7 effective) and the lower address side            |  |  |  |

|                                                                                 | BHE#      | Byte High Enable                  | Output       | (DB8–DB15 effective), respectively.  For external device access, it indicates that the upper byte data (DB0–DB7) is valid.                                                                                                                                                                                                                                                  |                                                                                |                                                                                                      |  |  |  |

|                                                                                 | BLE#      | Byte Low Enable                   | Output       | For externa<br>DB15) is va                                                                                                                                                                                                                                                                                                                                                  |                                                                                | ccess, it indicates that the lower byte data (DB8-                                                   |  |  |  |

|                                                                                 | WAIT#     | Wait                              | Input        |                                                                                                                                                                                                                                                                                                                                                                             | ut is low v                                                                    | when the M32R accesses external devices, the                                                         |  |  |  |

|                                                                                 | HREQ#     | Hold request                      | Input        | This pin is                                                                                                                                                                                                                                                                                                                                                                 | used by ar                                                                     | n external device to request control of the external to a hold state when HREQ# input is pulled low. |  |  |  |

|                                                                                 | HACK#     | Hold acknowledge                  | Output       | This signal indicates to the external device that the M32R has entered a hold state and relinquished control of the external bus.                                                                                                                                                                                                                                           |                                                                                |                                                                                                      |  |  |  |

Note 1: In boot mode, the FP pin must be at the high level.

## **Under Development**

### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

Table 3. Description of Pin Function (2/3)

| Туре                    | Pin                       | Name                                                                                         | Input/Output | Function                                                                                                                                                                                                                                            |

|-------------------------|---------------------------|----------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multijunction timer     | TIN0, TIN3<br>TIN16-TIN23 | Timer input                                                                                  | Input        | Input pin for multijunction timer                                                                                                                                                                                                                   |

|                         | TO0<br>-TO20              | Timer output                                                                                 | Output       | Output pin for multijunction timer                                                                                                                                                                                                                  |

|                         | TCLK0<br>-TCLK3           | Timer clock                                                                                  | Input        | Clock input pin for multijunction timers.                                                                                                                                                                                                           |

| A-D<br>converter        | AVCC0                     | Analog power sup-<br>ply                                                                     | -            | AVCC0 is the power supply for the A-D0 converter. Connect AVCC0 to the power supply rail.                                                                                                                                                           |

|                         | AVSS0                     | Analog ground                                                                                | -            | AVSS0 is the analog ground for the A-D0 converters. Connect AVSS0 to ground.                                                                                                                                                                        |

|                         | AD0IN0<br>-AD0IN11        | Analog input                                                                                 | Input        | 16-channel analog input pins for the A-D0 converter in the first block.                                                                                                                                                                             |

|                         | VREF0                     | Reference voltage input                                                                      | Input        | VREF0 is the reference voltage input pin for the A-D0 converter.                                                                                                                                                                                    |

| Interrupt<br>controller | SBI#                      | System break inter-<br>rupt                                                                  | Input        | System break interrupt (SBI) input pin of the interrupt controller                                                                                                                                                                                  |

| Serial I/O              | SCLKIO/<br>SCLKOO         | UART trans-<br>mit/receive clock<br>output or CSIO<br>transmit/receive<br>clock input/output | Input/output | When Channel 0 is in UART mode: Clock output derived from BRG output by dividing it by 2 When Channel 0 is in CSIO mode: Transmit/receive clock input when external clock is selected Transmit/receive clock output when internal clock is selected |

|                         | SCLKI1/<br>SCLKO1         | UART trans-<br>mit/receive clock<br>output or CSIO<br>transmit/receive<br>clock input/output | Input/output | When Channel 1 is in UART mode: Clock output derived from BRG output by dividing it by 2 When Channel 1 is in CSIO mode: Transmit/receive clock input when external clock is selected Transmit/receive clock output when internal clock is selected |

|                         | TXD0                      | Transmit data                                                                                | Output       | Transmit data output pin of serial I/O channel 0                                                                                                                                                                                                    |

|                         | RXD0                      | Receive data                                                                                 | Input        | Receive data input pin of serial I/O channel 0                                                                                                                                                                                                      |

|                         | TXD1                      | Transmit data                                                                                | Output       | Transmit data output pin of serial I/O channel 1                                                                                                                                                                                                    |

|                         | RXD1                      | Receive data                                                                                 | Input        | Receive data input pin of serial I/O channel 1                                                                                                                                                                                                      |

|                         | TXD2                      | Transmit data                                                                                | Output       | Transmit data output pin of serial I/O channel 2                                                                                                                                                                                                    |

|                         | RXD2                      | Receive data                                                                                 | Input        | Receive data input pin of serial I/O channel 2                                                                                                                                                                                                      |

|                         | TXD3                      | Transmit data                                                                                | Output       | Transmit data output pin of serial I/O channel 3                                                                                                                                                                                                    |

|                         | RXD3                      | Receive data                                                                                 | Input        | Receive data input pin of serial I/O channel 3                                                                                                                                                                                                      |

## **Under Development**

### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

Table 3. Description of Pin Function (3/3)

| Туре         | Pin        | Name                 | Input/Output | Function                                                                    |

|--------------|------------|----------------------|--------------|-----------------------------------------------------------------------------|

| Real-time    | RTDTXD     | Transmit data        | Output       | Serial data output pin of the Real-time Debugger                            |

| Debugger     | RTDRXD     | Receive data         | Input        | Serial data input pin of the Real-time Debugger                             |

|              | RTDCLK     | Clock input          | Input        | Serial data transmit/receive clock input pin of the Real-time Debugger      |

|              | RTDACK     | Acknowledge          | Output       | This pin outputs a low pulse synchronously with the Real-time Debug-        |

|              |            |                      |              | ger's first clock of serial data output word. The low pulse width indicates |

|              |            |                      |              | the type of the command/data the Real-time Debugger has received.           |

| CAN          | CTX0,      | Transmit data        | Output       | Data output pin from CAN module.                                            |

|              | CTX1       |                      |              |                                                                             |

|              | CRX0,      | Receive data         | Input        | Data input pin to CAN module.                                               |

|              | CRX1       |                      |              |                                                                             |

| JTAG         | JTMS       | Test mode            | Input        | Test select input for controlling the test circuit's state transition       |

|              | JTCK       | Clock                | Input        | Clock input to the debugger module and test circuit.                        |

|              | JTRST      | Test reset           | Input        | Test reset input for initializing the test circuit asynchronously.          |

|              | JTDO       | Serial output        | Output       | Serial output of test instruction code or test data.                        |

|              | JTDI       | Serial input         | Input        | Serial input of test instruction code or test data.                         |

| Input/output | P00-P07    | Input/output port 0  | Input/output | Programmable input/output port.                                             |

| Port         | P10-P17    | Input/output port 1  | Input/output | Programmable input/output port.                                             |

| (Note 1)     | P20-P27    | Input/output port 2  | Input/output | Programmable input/output port.                                             |

|              | P30-P37    | Input/output port 3  | Input/output | Programmable input/output port.                                             |

|              | P41-P47    | Input/output port 4  | Input/output | Programmable input/output port.                                             |

|              | P61-P63    | Input/output port 6  | Input/output | Programmable input/output port.                                             |

|              | P70-P77    | Input/output port 7  | Input/output | Programmable input/output port.                                             |

|              | P82-P87    | Input/output port 8  | Input/output | Programmable input/output port.                                             |

|              | P93-P97    | Input/output port 9  | Input/output | Programmable input/output port.                                             |

|              | P100-P107  | Input/output port 10 | Input/output | Programmable input/output port.                                             |

|              | P110-P117  | Input/output port 11 | Input/output | Programmable input/output port.                                             |

|              | P124-P127  | Input/output port 12 | Input/output | Programmable input/output port.                                             |

|              | P130-P137  | Input/output port 13 | Input/output | Programmable input/output port.                                             |

|              | P150, P153 | Input/output port 15 | Input/output | Programmable input/output port.                                             |

|              | P174, P175 | Input/output port 17 | Input/output | Programmable input/output port.                                             |

|              | P220, P221 | Input/output port 22 | Input/output | Programmable input/output port.                                             |

|              | P224, P225 |                      |              | (However, P221 is an input-only port)                                       |

Note 1: Input/output port 5 is reserved for future use. Input/output ports 14,16,18, 20 and 21 do not exist.

### **Under Development**

#### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

#### **Outline of the CPU core**

The 32182 Group is built around the M32R RISC CPU core, and has the instruction set common to all of the M32R family microcomputers. To achieve high-precision arithmetic operation, this microcomputer additionally incorporates a fully IEEE754 compliant, single-precision FPU.

Instructions are processed in five pipelined stages consisting of instruction fetch, decode, execution, memory access, and write back. Thanks to its "out-of-order-completion" mechanism, the M32R CPU allows clock cycle to realize efficient instruction execution control.

The M32R-FPU internally contains sixteen 32-bit generalpurpose registers. The instruction set consists of 100 discrete instructions, which come in either 16-bit or 32-bit instruction format. Use of the 16-bit instruction format helps to reduce the program code size. Also, the availability of 32-bit instructions facilitates programming and increases the performance at the same clock speed, as compared to architectures with segmented address spaces.

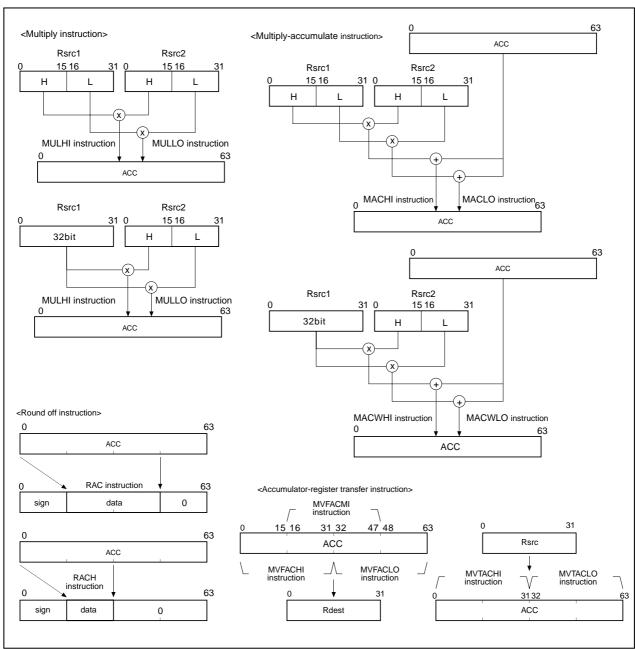

### Multiply-Accumulate instructions comparable to DSP

The M32R-FPU contains a multiplier/accumulator that can execute 32-bit  $\times$  16-bit in one cycle. Therefore, it executes a 32-bit  $\times$  32-bit integer multiplication instruction in three cycles

Also, the M32R-FPU supports the following four multiply-Accumulate instructions (or multiplication instructions) for DSP function use.

- (1) 16 high-order register bits  $\times$  16 high-order register bits

- (2) 16 low-order register bits  $\times$  16 low-order register bits

- (3) All 32 register bits  $\times$  16 high-order register bits

- (4) All 32 register bits  $\times$  16 low-order register bits

Furthermore, the M32R-FPU has instructions for rounding the value stored in the accumulator to 16 or 32-bit, and instructions for shifting the accumulator value to adjust digits before storing in a register. Because these instructions also can be executed in one cycle, DSP comparable data processing capability can be obtained by using them in combination with high-speed data transfer instructions such as Load & Address Update or Store & Address Update.

#### **FPU** instructions (12 instructions)

The M32R-FPU supports single-precision, floating-point arithmetic operations fully compliant with IEEE754 standard. More specifically, it supports all of the following five exceptions and four rounding modes. Because the general-purpose registers are used for floating-point arithmetic, data transfer overhead is reduced.

- Five exceptions (invalid operation, division by zero, overflow, underflow, and inexact)

- Four rounding modes (round toward nearest, round toward zero, round toward +∞, round toward -∞)

Also included are the floating-point multiply and add (FMADD) and floating-point multiply and subtract (FMSUB) instructions suitable for butterfly operation in FFT.

### **Extended instructions (5 instructions)**

The M32R-FPU has several instructions implemented in it as extended instructions such as those to set, clear, and test bits, those to set and clear data in the processor status register, and those to automatically increment the address in which to store a halfword.

#### Address space

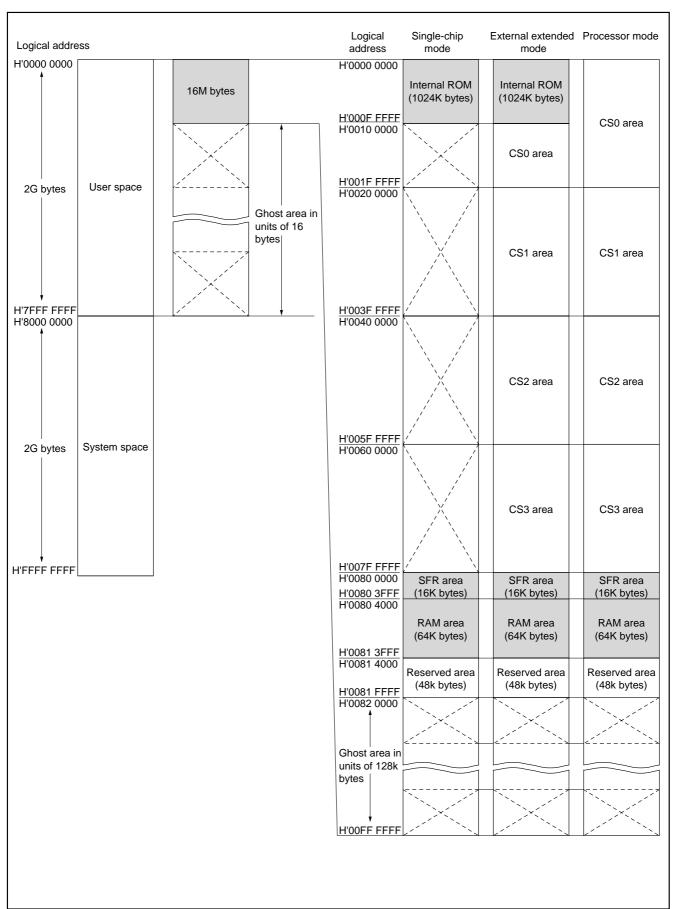

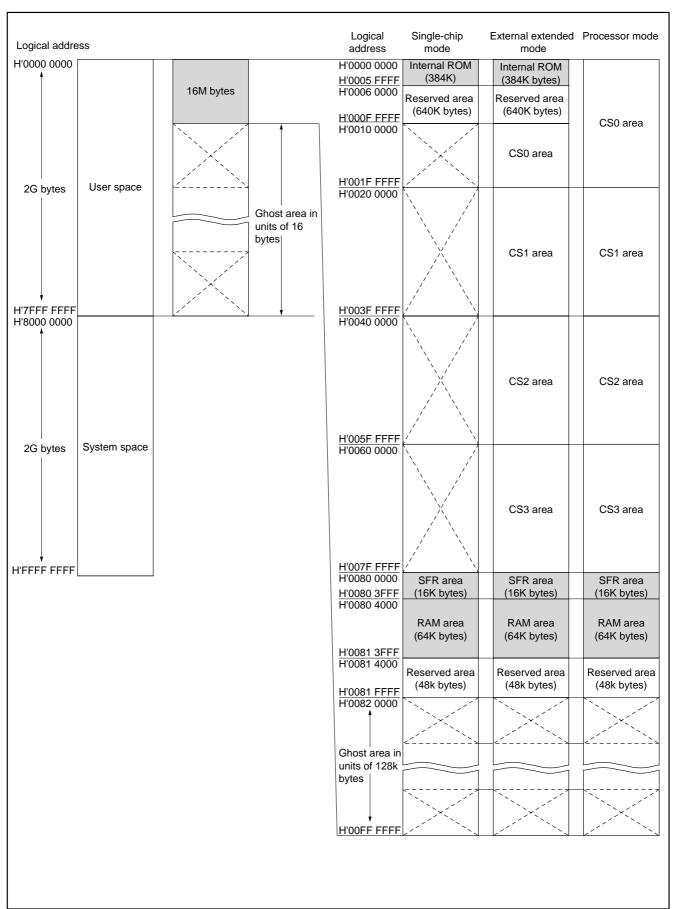

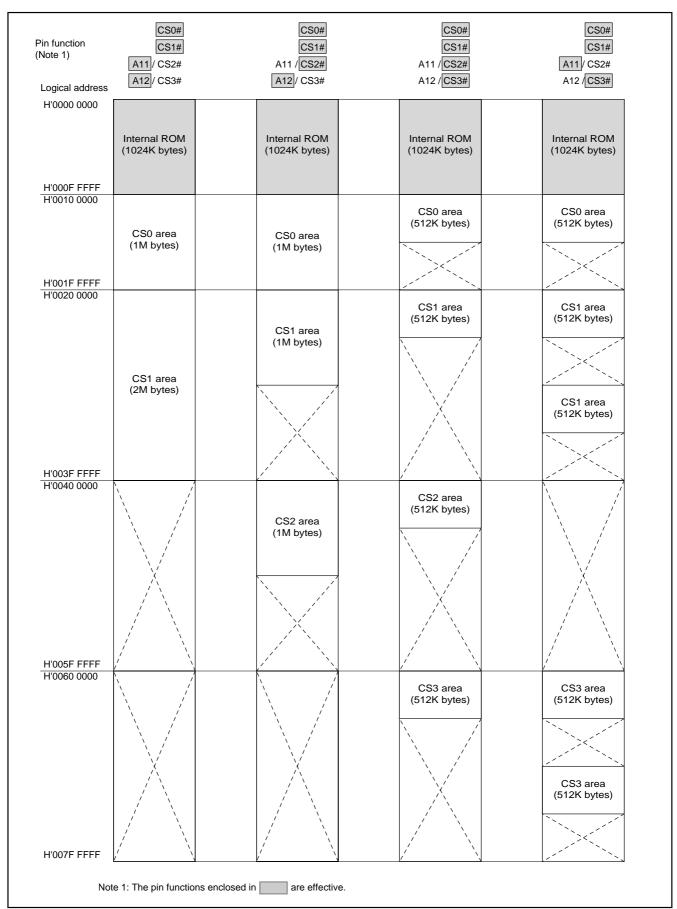

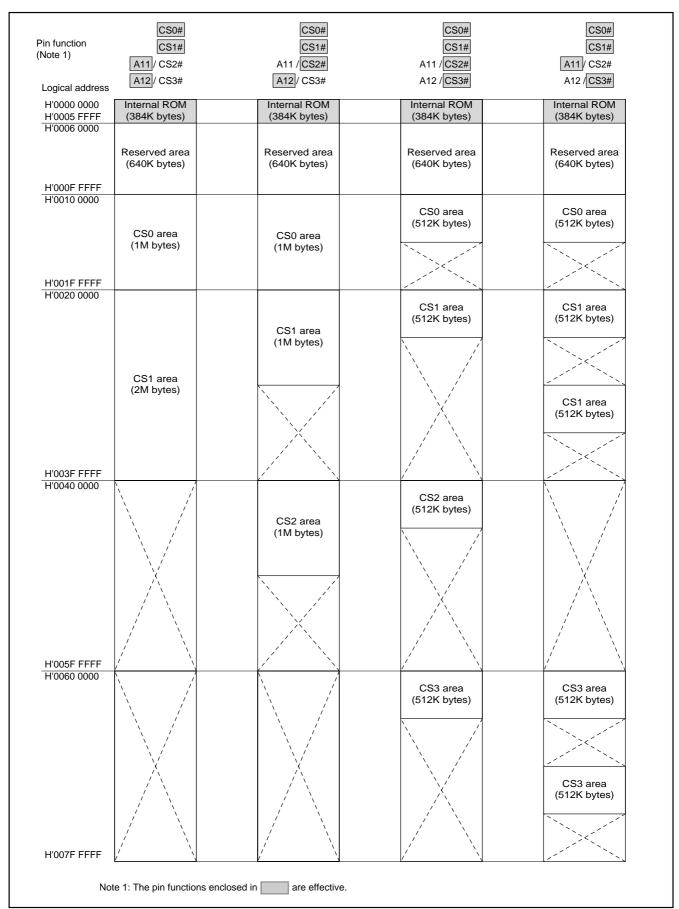

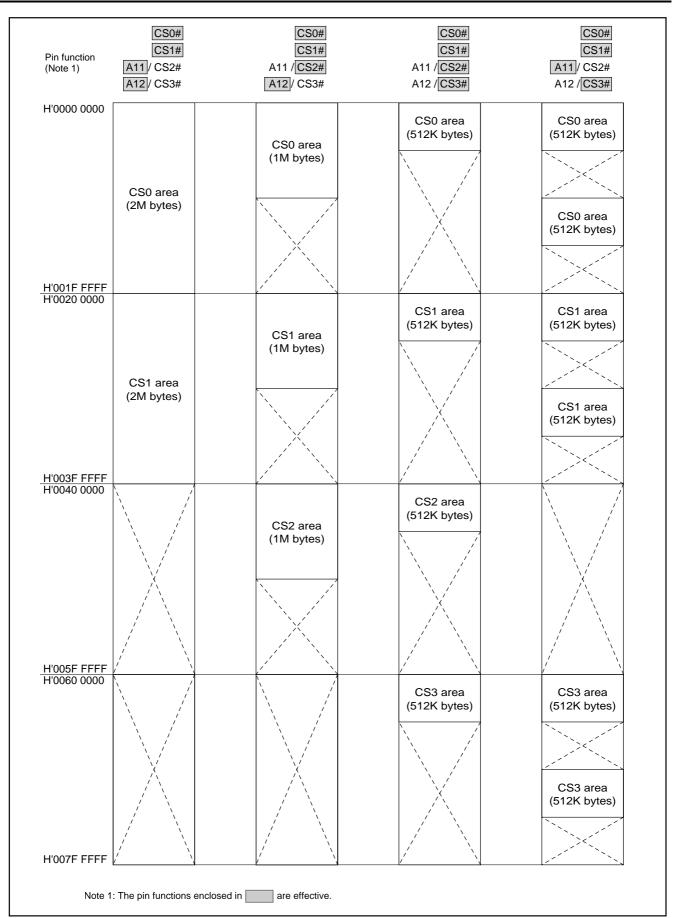

The 32182 Group's logical address is always handled in width of 32-bit, providing a linear address space of up to 4G bytes. The 32182's address space is divided into the following spaces.

#### **User space**

A 2G-byte area from H'0000 0000 to H'7FFF FFFF is the user space. Located in this space are the user ROM area, external extended area, internal RAM area, and SFR (Special Function Register) area (internal peripheral I/O registers). Of these, the user ROM area and external extended area are located differently depending on mode settings.

### System space

A 2G-byte area from H'8000 0000 to H'FFFF FFFF is the system area. This space is reserved for use by development tools such as an in-circuit emulator and debug monitor, and cannot be used by the user.

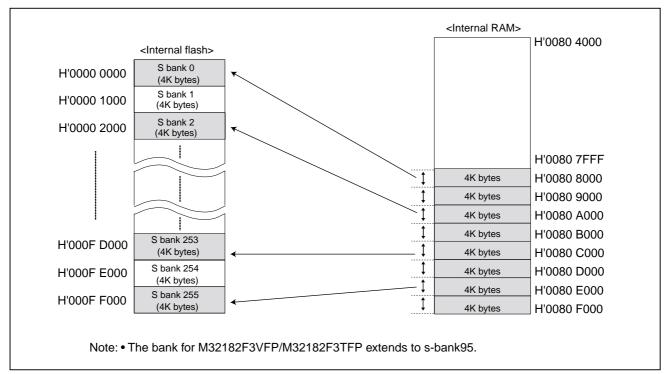

#### **Built-in flash memory and RAM**

The M32182F8VFP/M32182F8TFP contains 1024K bytes flash memory and 64K bytes RAM, the M32182F3VFP/M32182F3TFP contains 384K bytes flash memory and 64K bytes RAM.

The internal flash memory can be programmed while being mounted on the printed circuit board (on-board programming). Use of flash memory allows the same chip as those used in mass production to be used beginning with the development stage. This means that system development can be proceeded without having to change the printed circuit boards during the entire course, from prototype to mass production.

## **Under Development**

Figure 4. Address space of the M32182F8VFP/M32182F8TFP

## **Under Development**

Figure 5. Address space of the M32182F3VFP/M32182F3TFP

## **Under Development**

Figure 6. Internal ROM and External Extended Area when External Extended Mode (M32182F8VFP/M32182F8TFP)

## **Under Development**

Figure 7. Internal ROM and External Extended Area when External Extended Mode (M32182F3VFP/M32182F3TFP)

## **Under Development**

Figure 8. External Extended Area when Processor Mode

## **Under Development**

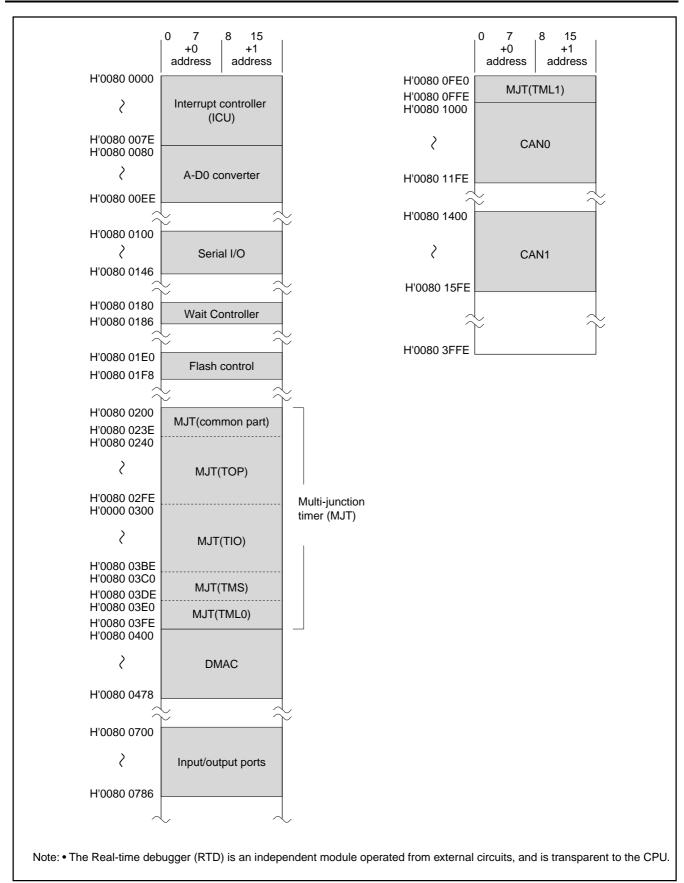

Figure 9. SFR Area

## **Under Development**

### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

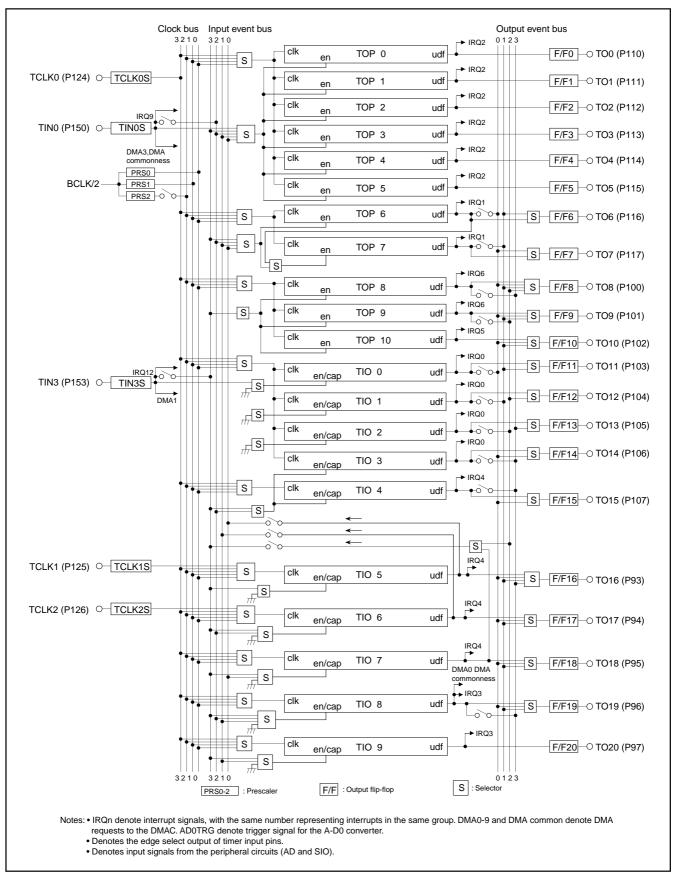

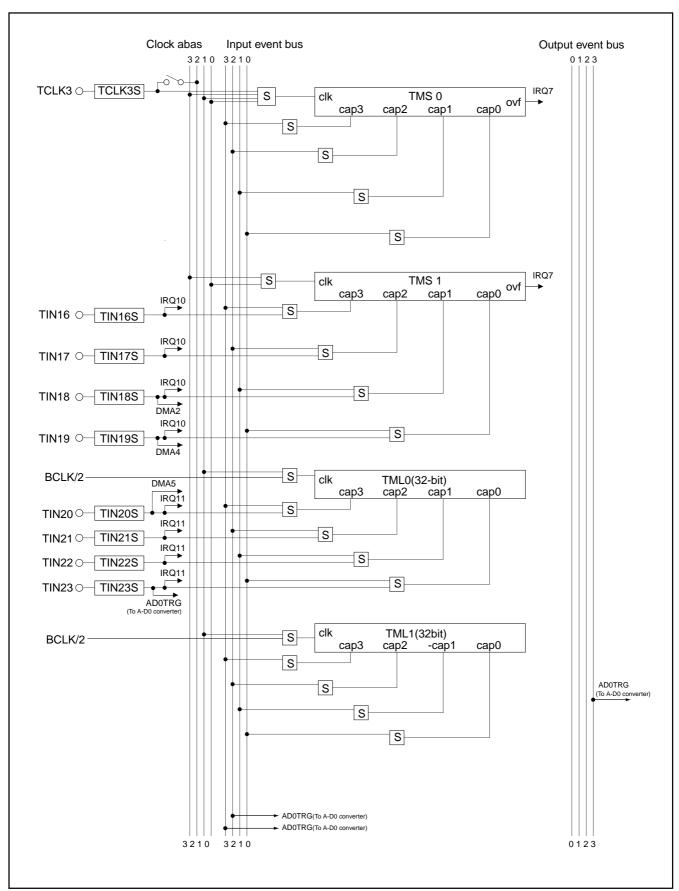

### **Built-in 37-channel multijunction timers (MJT)**

The microcomputer contains a total of 37 channels of multijunction timers consisting of 11 channels of 16-bit output related timers, 10 channels of 16-bit input/output related timers, 8 channels of 16-bit input related timers, 8 channels of 32-bit input related timers. Each timer has multiple operation modes to choose from, depending on the purposes of use. Also, the multijunction timers internally have a clock bus, input event bus, and an output event bus, so that multiple timers can be used in combination allowing for a flexible timer configuration. The output related timers have a correcting function that allows the timer's count value to be incremented or decremented as necessary while count is in progress, making real-time output control possible.

Table 4. Outline of the MJT

| Name                            | Туре                                                    | Number of<br>channels | Contents                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|---------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOP<br>(Timer Output)           | Output related 16-bit timer (down-counter)              | 11                    | One of three output modes is selected in software. <with correcting="" function=""> • Single-shot output mode • Delayed single-shot output mode <without correcting="" function=""> • Continuous output mode</without></with>                                                                                                                         |

| TIO<br>(Timer Input<br>Output)  | Input/output related<br>16-bit timer (down-<br>counter) | 10                    | One of three input modes and four output modes is selected in software. <input mode=""/> • Measure clear input mode • Measure free-run input mode • Noise processing input mode <output correcting="" function="" mode="" without=""> • PWM output mode • Single-shot output mode • Delayed single-shot output mode • Continuous output mode</output> |

| TMS<br>(Timer Measure<br>Small) | Input related<br>16-bit timer (up-counter)              | 8                     | 16-bit input measure timer.                                                                                                                                                                                                                                                                                                                           |

| TML<br>(Timer Measure<br>Large) | 32-bit timer (up-counter)                               | 8                     | 32-bit input measure timer.                                                                                                                                                                                                                                                                                                                           |

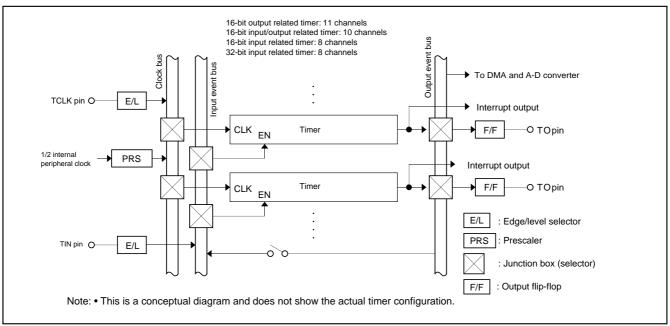

## **Under Development**

Figure 10. Conceptual Diagram of the Multijunction Timers (MJT)

## **Under Development**

Figure 11. Block Diagram of MJT (1/3)

## **Under Development**

Figure 12. Block Diagram of MJT (2/3)

## **Under Development**

Figure 13. Block Diagram of MJT (3/3)

### **Under Development**

#### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

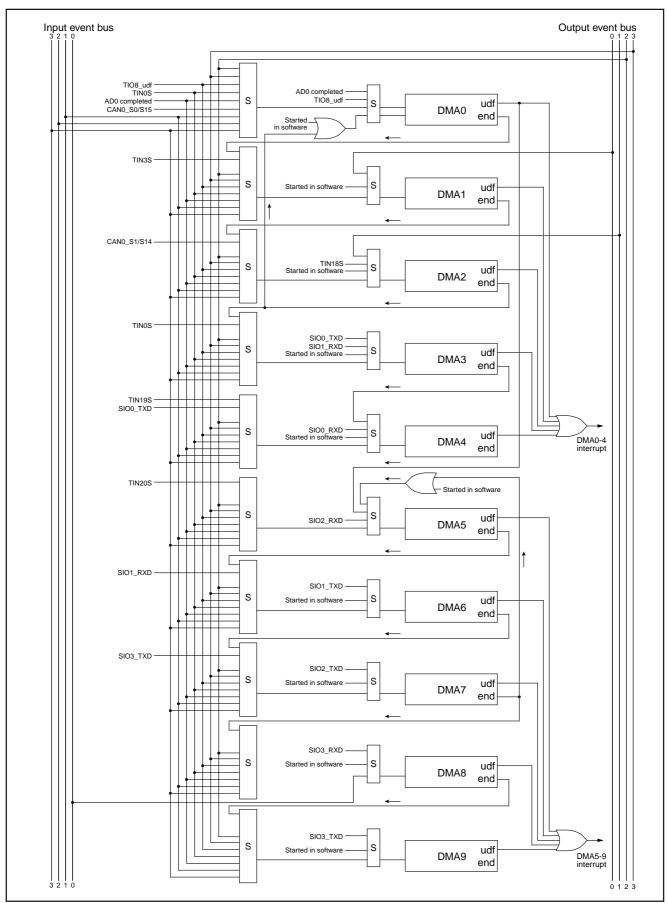

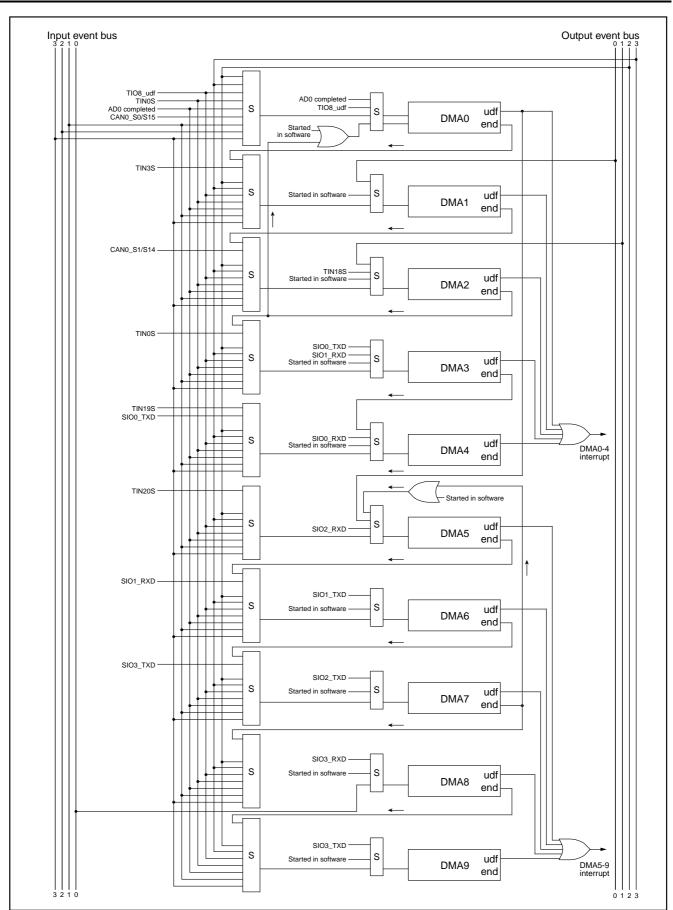

#### **Built-in 10-Channel DMAC**

The microcomputer contains 10 channels of DMAC, allowing for data transfer between internal peripheral I/Os, between internal RAM and internal peripheral I/O, and between internal RAMs.

DMA transfer requests can be issued from the user-created software, as well as can be triggered by a signal generated by the internal peripheral I/O (A-D converter, timer, or serial I/O).

The microcomputer also supports cascaded connection between DMA channels (starting DMA transfer on a channel at end of transfer on another channel). This makes advanced transfer processing possible without causing any additional CPU load.

Table 5. Outline of the DMAC

| Item                                | Content                                                                                                  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------|

| Number of channels                  | 10 channels                                                                                              |

| Transfer request                    | Software trigger                                                                                         |

|                                     | <ul> <li>Request from internal peripheral I/O: A-D converter, timer, or serial I/O (reception</li> </ul> |

|                                     | completed, transmit buffer empty)                                                                        |

|                                     | Cascaded connection between DMA channels possible (Note 1)                                               |

| Maximum number of times transferred | 65536 times                                                                                              |

| Transferable address space          | 64K bytes (address space from H'0080 0000 to H'0080 FFFF)                                                |

|                                     | <ul> <li>Transfers between internal peripheral I/Os, between internal RAM and internal</li> </ul>        |

|                                     | peripheral IO, and between internal RAMs are supported                                                   |

| Transfer data size                  | 16-bit or 8-bit                                                                                          |

| Transfer method                     | Single transfer DMA (control of the internal bus is relinquished for each transfer per-                  |

|                                     | formed), dual-address transfer                                                                           |

| Transfer mode                       | Single transfer mode                                                                                     |

| Direction of transfer               | One of three modes can be selected for the source and destination of transfer:                           |

|                                     | Address fixed                                                                                            |

|                                     | Address increment                                                                                        |

|                                     | 32-channel ring buffer                                                                                   |

| Channel priority                    | Channel 0 > channel 1 > channel 2 > channel 3 > channel 4 > channel 5 > channel                          |

|                                     | 6 > channel 7 > channel 8 > channel 9 (Fixed priority)                                                   |

| Maximum transfer rate               | 13.3M bytes per second (when internal peripheral clock = 20 MHz)                                         |

| Interrupt request                   | Group interrupt request can be generated when each transfer count register under-                        |

|                                     | flows                                                                                                    |

Note 1: The following DMA channels can be cascaded.

DMA transfer on channel 1 started at end of one DMA transfer on channel 0

DMA transfer on channel 5 started at completion of all DMA transfers on channel 0 (transfer count register underflow)

DMA transfer on channel 2 started at end of one DMA transfer on channel 1

DMA transfer on channel 0 started at end of one DMA transfer on channel 2

DMA transfer on channel 3 started at end of one DMA transfer on channel 2

DMA transfer on channel 4 started at end of one DMA transfer on channel 3

DMA transfer on channel 6 started at end of one DMA transfer on channel 5 DMA transfer on channel 7 started at end of one DMA transfer on channel 6

DMA transfer on channel 5 started at end of one DMA transfer on channel 7

DMA transfer on channel 8 started at end of one DMA transfer on channel 7

DMA transfer on channel 9 started at end of one DMA transfer on channel 8

## **Under Development**

Figure 14. Block Diagram of DMAC

## **Under Development**

#### SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

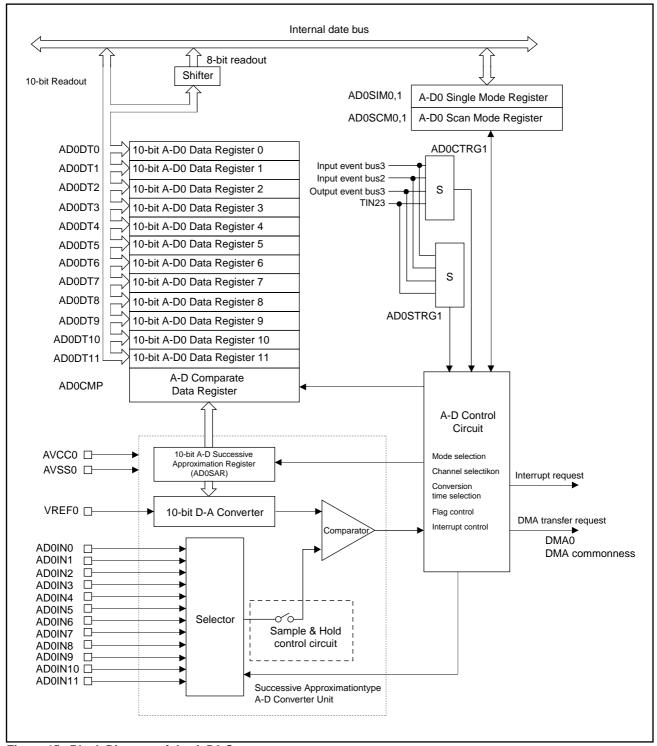

#### 12-channel A-D Converters

The microcomputer contains 12-channel A-D converters with 10-bit resolution. In addition to single conversion on each channel, continuous A-D conversion on a combined group of N (N = 1-12) channels is possible. The A-D converted value can be read out in either 10-bit or 8-bit.

In addition to ordinary A-D conversion, the converters support comparator mode in which the set value and A-D converted value are compared to determine which is larger or smaller than the other.

Moreover, there is also Sample & hold function, input voltage is sampled, when A-D conversion is started, and the A-D conversion of the sampling voltage is carried out.

Since there is no invalid domain near [which becomes a problem by the external operational amplifier etc.] VCCE/VSS, conversion by the full range is possible in this sample & hold circuit. When A-D conversion is finished, the converters can generate a DMA transfer request, as well as an interrupt.

The A-D converters are interfaced using a dedicated power supply to allow for connections to the peripheral circuits operating with 5  $\rm V.$

Table 6. Outline of the A-D Converters

| Item                                           | Content                                                                                           |                                                                                   |                      |            |                 |            |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|------------|-----------------|------------|--|--|--|

| Analog input                                   | 12-channel                                                                                        |                                                                                   |                      |            |                 |            |  |  |  |

| A-D conversion method                          | Successive approximation method                                                                   |                                                                                   |                      |            |                 |            |  |  |  |

| Resolution                                     | 10-bit (Conversion results can be read out in either 10 or 8-bit)                                 |                                                                                   |                      |            |                 |            |  |  |  |

| Absolute accuracy (conditions:                 | During low speed mode: Normal mode: ± 2 LSB, double speed mode: ± 2 LSB (Note 1)                  |                                                                                   |                      |            |                 |            |  |  |  |

| Ta = 25°C, AVCC0, 1 =<br>VREF0, 1 = 5.12 V)    | During high speed mode: N                                                                         | During high speed mode: Normal mode: ± 3 LSB, double speed mode: ± 3 LSB (Note 1) |                      |            |                 |            |  |  |  |

| Conversion mode                                | A-D conversion mode, con                                                                          | nparator mode                                                                     |                      |            |                 |            |  |  |  |

| Operation mode                                 | Single mode, scan mode                                                                            |                                                                                   |                      |            |                 |            |  |  |  |

| Scan mode                                      | Single-shot scan mode, co                                                                         | ntinuous scan r                                                                   | node                 |            |                 |            |  |  |  |

| Special mode                                   | Single mode forcible execugle mode execution, conve                                               |                                                                                   | n mode operation,    | scan m     | ode start after | r the sin- |  |  |  |

| Sample & hold function                         | Input voltage is sampled w sampling voltage.                                                      | hen A-D conver                                                                    | rsion is started, an | d it is A  | A-D conversion  | about      |  |  |  |

| Conversion start trigger                       | Software start                                                                                    | Started by set                                                                    | ting A-D conversion  | on start   | bit to 1        |            |  |  |  |

|                                                | Hardware start                                                                                    |                                                                                   | ent bus 2, MJT inp   |            |                 | output     |  |  |  |

| Conversion Speed f(BCLK) : Internal peripheral | During single mode<br>(Unavailable for Sample<br>& Hold<br>Available for Normal<br>Sample & Hold) | Low-speed mode                                                                    | Normal               | 299        | ×1/f(BCLK)      | (Note 2)   |  |  |  |

| clock operating frequency                      |                                                                                                   |                                                                                   | Double speed         | 173        | ×1/f(BCLK)      |            |  |  |  |

|                                                |                                                                                                   | High-speed mode                                                                   | Normal               | 131        | ×1/f(BCLK)      |            |  |  |  |

|                                                |                                                                                                   |                                                                                   | Double speed         | 89         | ×1/f(BCLK)      |            |  |  |  |

|                                                | During single mode<br>(Available for High-speed                                                   | Low-speed mode                                                                    | Normal               | 191        | ×1/f(BCLK)      |            |  |  |  |

|                                                | Sample & Hold)                                                                                    |                                                                                   | Double speed         | 101        | ×1/f(BCLK)      |            |  |  |  |

|                                                | , , , , , , , , , , , , , , , , , , , ,                                                           | High-speed mode                                                                   | Normal               | 95         | ×1/f(BCLK)      |            |  |  |  |

|                                                |                                                                                                   |                                                                                   | Double speed         | 53         | ×1/f(BCLK)      |            |  |  |  |

|                                                | During comparator mode                                                                            | Low-speed mode                                                                    | Normal               | 47         | ×1/f(BCLK)      |            |  |  |  |